ABSTRACT

Title of dissertation: HEAP DATA ALLOCATION TO

SCRATCH-PAD MEMORY IN EMBEDDED

SYSTEMS

Angel Dominguez

Doctor of Philosophy, 2007

Dissertation directed by: Professor Rajeev K. Barua

Department of Electrical and Computer Engineering

This thesis presents the first-ever compile-time method for allocating a portion of a program's dynamic data to scratch-pad memory. A scratch-pad is a fast directly addressed compiler-managed SRAM memory that replaces the hardware-managed cache. It is motivated by its better real-time guarantees vs cache and by its significantly lower overheads in access time, energy consumption, area and overall runtime. Dynamic data refers to all objects allocated at run-time in a program, as opposed to static data objects which are allocated at compile-time. Existing compiler methods for allocating data to scratch-pad are able to place only code, global and stack data (static data) in scratch-pad memory; heap and recursive-function objects(dynamic data) are allocated entirely in DRAM, resulting in poor performance for these dynamic data types. Runtime methods based on software caching can place data in scratch-pad, but because of their high overheads from software address translation, they have not been successful, especially for dynamic data.

In this thesis we present a dynamic yet compiler-directed allocation method for

dynamic data that for the first time, (i) is able to place a portion of the dynamic data in scratch-pad; (ii) has no software-caching tags; (iii) requires no run-time per-access extra address translation; and (iv) is able to move heap data back and forth between scratch-pad and DRAM to better track the program's locality characteristics. With our method, code, global, stack and heap variables can share the same scratch-pad. When compared to placing all dynamic data variables in DRAM and only static data in scratch-pad, our results show that our method reduces the average runtime of our benchmarks by 22.3%, and the average power consumption by 26.7%, for the same size of scratch-pad fixed at 5% of total data size. Significant savings in runtime and energy were also observed when compared against cached memory organizations, showing our method's success with SPM placement of dynamic data under constrained memory sizes.

# HEAP DATA ALLOCATION TO SCRATCH-PAD MEMORY IN EMBEDDED SYSTEMS

by

#### Angel Dominguez

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2007

Advisory Committee:

Professor Rajeev K. Barua, Chair/Advisor

Professor Manoj Franklin

Professor Shuvra S. Bhattacharrya

Professor Peter Petrov

Professor Chau-Wen Tseng

© Copyright by Angel Dominguez 2007

### Table of Contents

| Lis | st of 1       | Figures                                                | iv      |

|-----|---------------|--------------------------------------------------------|---------|

| 1   | Intro         | oduction Organization of Thesis                        | 1<br>11 |

|     |               |                                                        | 11      |

| 2   | Emb           | pedded Systems and Software Development                | 13      |

|     | 2.1           | V                                                      | 14      |

|     | 2.2           | S I                                                    | 22      |

|     | 2.3           | Embedded Software Development                          | 26      |

|     | 2.4           | C Language Compilers                                   | 33      |

|     | 2.5           | Heap Data Allocation                                   | 39      |

|     | 2.6           | Recursive Functions                                    | 44      |

| 3   | Prev          | vious Work on SPM allocation                           | 47      |

|     | 3.1           | Overview of Related Research                           | 47      |

|     | 3.2           | Static SPM Allocation Methods                          | 48      |

|     | 3.3           | Dynamic SPM Allocation Techniques                      | 53      |

|     | 3.4           | Existing Methods For Dynamic Program Data              | 58      |

|     | 3.5           | Heap-to-Stack Conversion Techniques                    | 60      |

|     | 3.6           | Memory Hierarchy Research                              | 62      |

|     | 3.7           | Dynamic Memory Manager Research                        | 68      |

|     | 3.8           | Other Related Methods                                  | 69      |

| 5   | Dvn           | amic allocation of static program data                 | 73      |

|     | $5.1^{\circ}$ | Overview for static program allocation                 | 74      |

|     | 5.2           | The Dynamic Program Region Graph                       |         |

|     | 5.3           | Allocation Method for Code, Stack and Global Objects   |         |

|     | 5.4           | Algorithm Modifications                                |         |

|     | 5.5           | Layout and Code Generation                             |         |

|     | 5.6           | Summary of results                                     |         |

| 5   | Dvn           | amic program data                                      | 106     |

|     | 5.1           | Understanding dynamic data in software                 |         |

|     | 5.2           | Obstacles to optimizing software with dynamic data     |         |

|     | 5.3           | Creating the DPRG with dynamic data                    |         |

| 6   | Com           | npiler allocation of dynamic data                      | 131     |

| O   | 6.1           | Overview of our SPM allocation method for dynamic data |         |

|     | 6.2           | Preparing the DPRG for allocation                      |         |

|     | 6.3           | Calculating Heap Bin Allocation Sizes                  |         |

|     | 6.4           | Overview of the iterative portion                      |         |

|     | 6.5           | Transfer Minimizations                                 |         |

|     | 6.6           |                                                        | 44      |

|     | 6.7<br>6.8<br>6.9<br>6.10                             | Memory Layout Technique for Address Assignment                                                                                                                                                                                                                                                                                                           | 153<br>155                                                  |

|-----|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 7   | Robi<br>7.1<br>7.2<br>7.3<br>7.4                      | General Optimizations                                                                                                                                                                                                                                                                                                                                    | 164<br>171                                                  |

| 8   | Meth<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7 | Target Hardware Platform Software Platform Requirements Compiler Implementation Simulation Platform Benchmark Overview Benchmark Classes Benchmark Suite                                                                                                                                                                                                 | 199<br>203<br>211<br>215<br>216                             |

| 9   | 9.1<br>9.2<br>9.3<br>9.4<br>9.5                       | Dynamic Heap Allocation Results  9.1.1 Runtime and energy gain  9.1.2 Transfer Method Comparison  9.1.3 Reduction in Heap DRAM Accesses  9.1.4 Effect of varying SPM size  Unknown-size Heap Allocation  Recursive Function Allocation  Comparison with caches  Profile Sensitivity  9.5.1 Non-Profile Input Variation  Code Allocation  Code Allocation | 224<br>228<br>232<br>235<br>236<br>239<br>247<br>254<br>258 |

| 10  | 10.1<br>10.2                                          | Primary Heap Allocation Results                                                                                                                                                                                                                                                                                                                          | 274                                                         |

| Bil | oliogr                                                | aphy                                                                                                                                                                                                                                                                                                                                                     | 287                                                         |

## List of Figures

| 1.1  | Example of heap allocation using our method                                                                                                                    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1  | Diagram of typical desktop computer                                                                                                                            |

| 2.2  | Diagram of typical embedded computer                                                                                                                           |

| 2.3  | Memory types common to embedded platforms                                                                                                                      |

| 2.4  | Comparison between popular embedded memory types                                                                                                               |

| 2.5  | Diagram of the Intel StrongARM embedded cpu                                                                                                                    |

| 2.6  | Compilation of an application from source files                                                                                                                |

| 2.7  | Compiler view of program memory                                                                                                                                |

| 2.8  | Sample memory layout for an embedded application 41                                                                                                            |

| 2.9  | Heap manager example                                                                                                                                           |

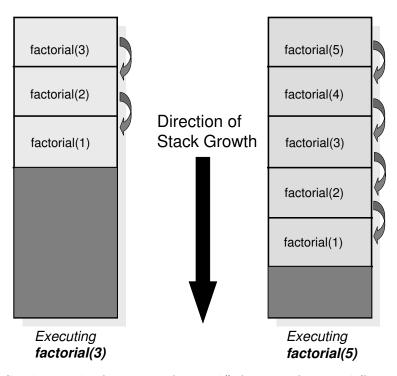

| 2.10 | Stack growth of a recursive function                                                                                                                           |

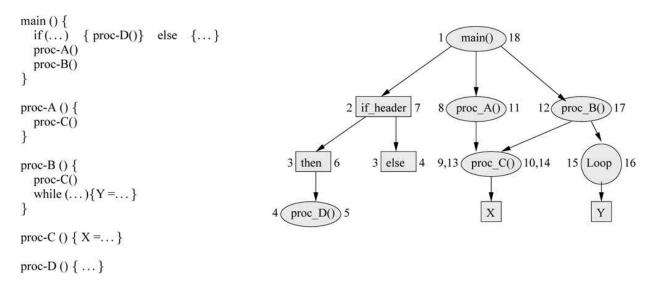

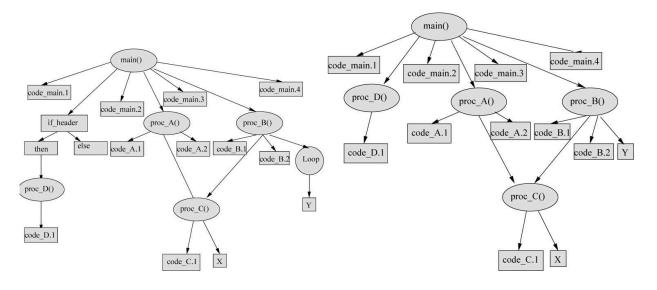

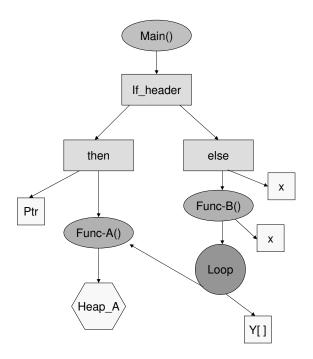

| 5.1  | DPRG created for a sample program                                                                                                                              |

| 5.2  | Algorithm for dynamic allocation of static program data 85 $$                                                                                                  |

| 5.3  | DPRG enhanced with code regions                                                                                                                                |

| 5.1  | Memory map for a typical ARM application                                                                                                                       |

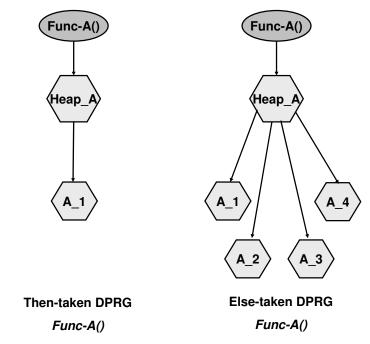

| 5.2  | Example of a recursive data structure                                                                                                                          |

| 5.3  | Example program fragment                                                                                                                                       |

| 5.4  | DPRG showing a heap allocation site                                                                                                                            |

| 5.5  | DPRG for a sample function with heap data                                                                                                                      |

| 6.1  | Algorithm for dynamic allocation of heap data                                                                                                                  |

| 6.2  | Calculating heap bin sizes for allocation                                                                                                                      |

| 6.3  | Allocation scenario for an example program $\dots \dots \dots$ |

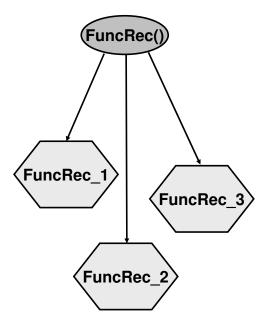

| 7.1  | DPRG of a recursive function                                                 |

|------|------------------------------------------------------------------------------|

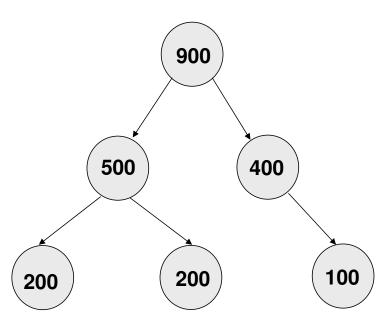

| 7.2  | Binary tree showing access frequency                                         |

| 7.3  | Sample Program containing unknown-size heap allocation 177                   |

| 7.4  | Sample Function containing unknown-size heap allocation 189                  |

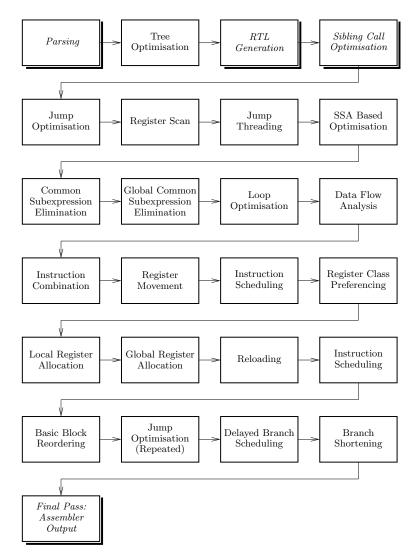

| 8.1  | GCC compiler flow for an application                                         |

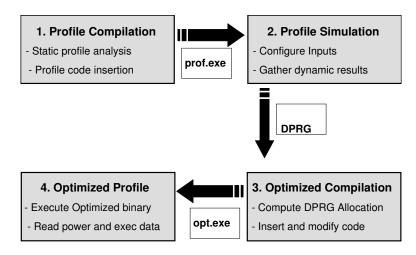

| 8.2  | Main stages of our allocation algorithm                                      |

| 8.3  | Benchmark Suite Information - Part 1                                         |

| 8.4  | Benchmark Suite Information - Part 2                                         |

| 8.5  | Benchmark Suite Information - Part 3                                         |

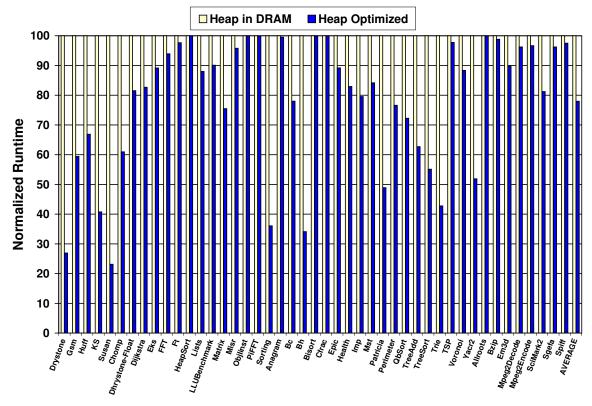

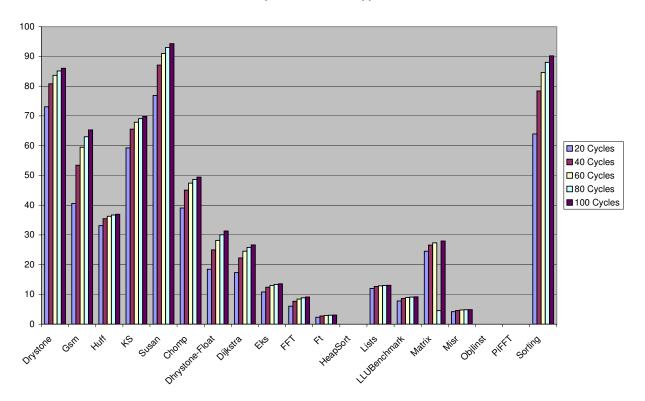

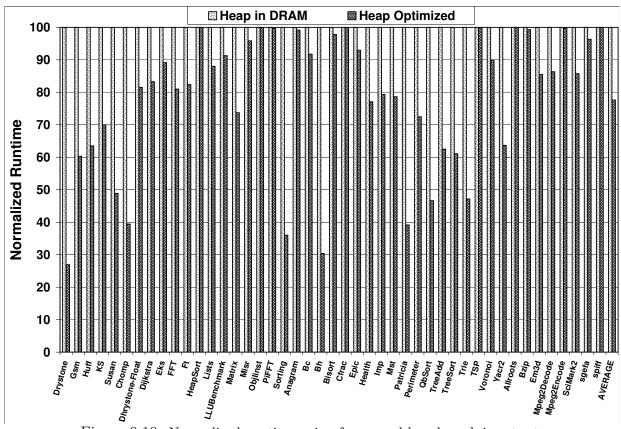

| 9.1  | Runtime gain from our method for the default scenario                        |

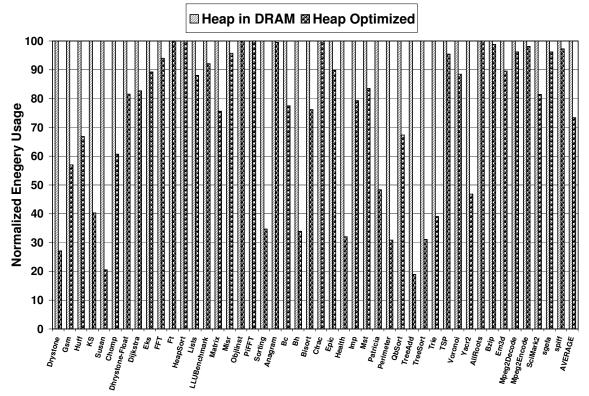

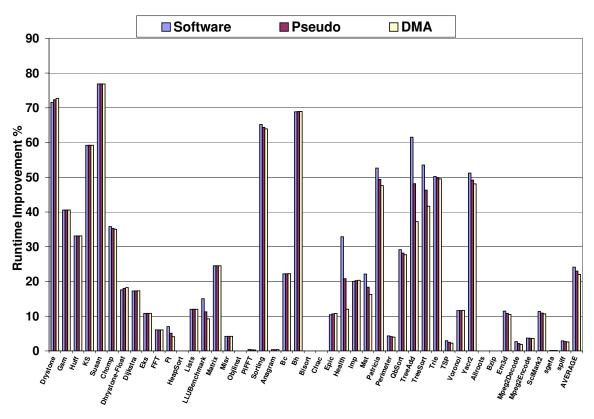

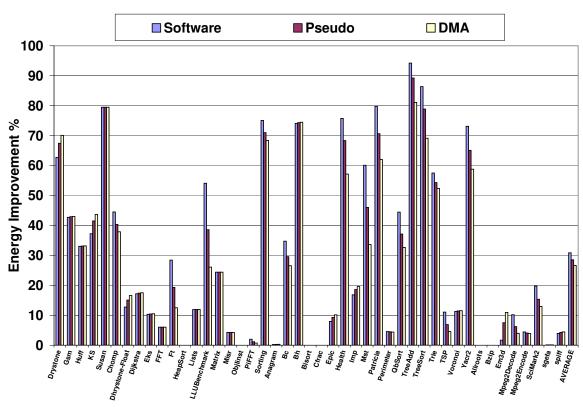

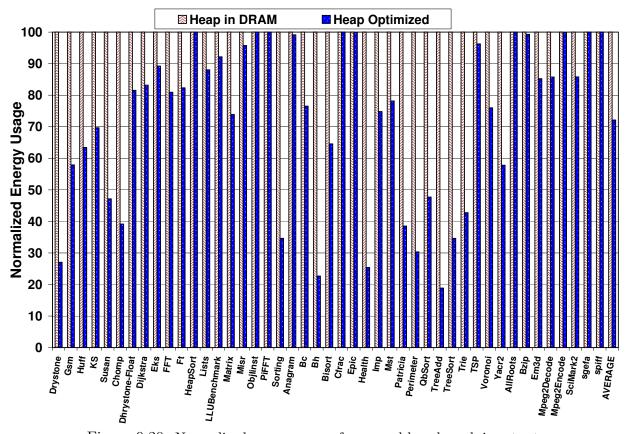

| 9.2  | Energy savings from our method for the default scenario                      |

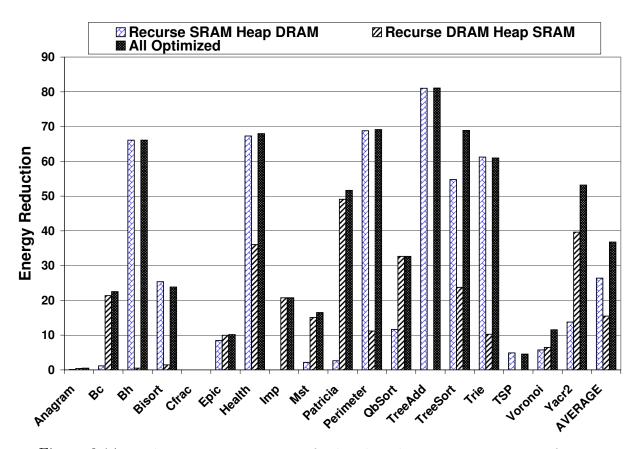

| 9.3  | Runtime results from using different transfer methods                        |

| 9.4  | Power consumption using different transfer methods                           |

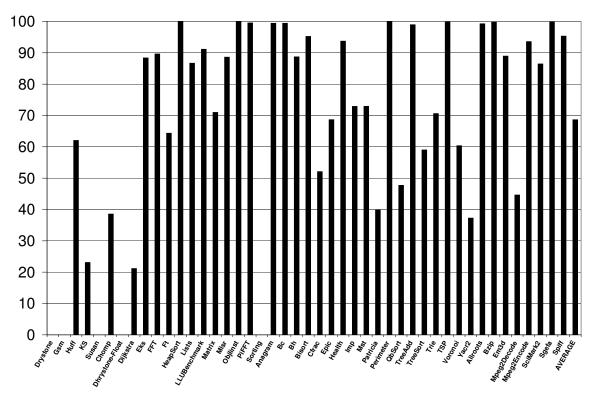

| 9.5  | Percentage of heap accesses going to DRAM after allocation 232               |

| 9.6  | Effects of varying DRAM latency on runtime gain(Part 1) 233                  |

| 9.7  | Effects of varying DRAM latency on runtime gain(Part 2) 234                  |

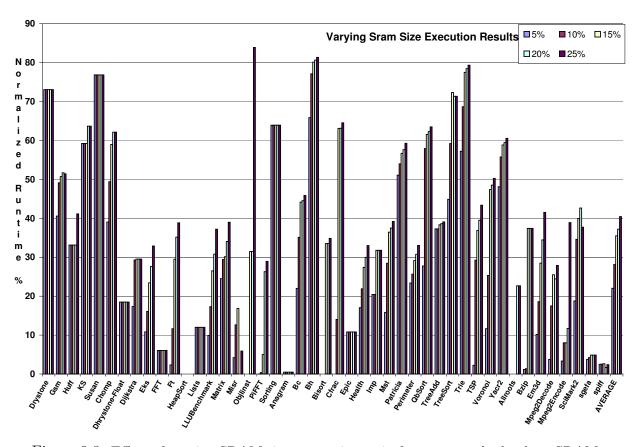

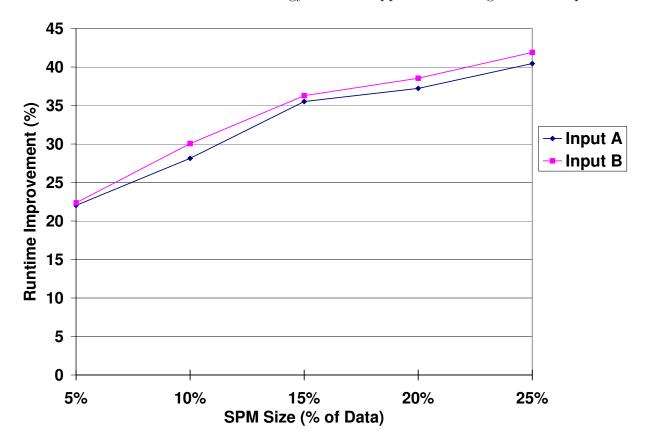

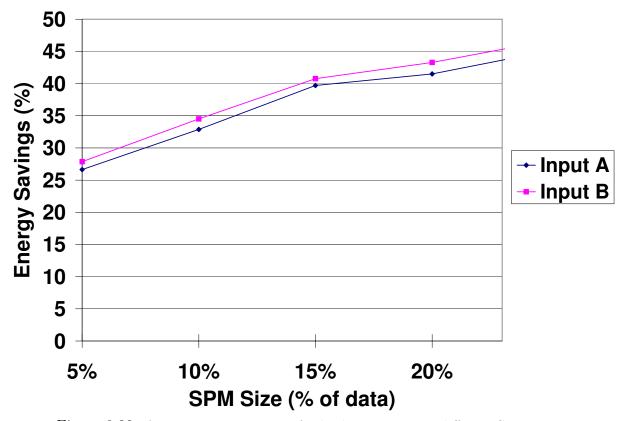

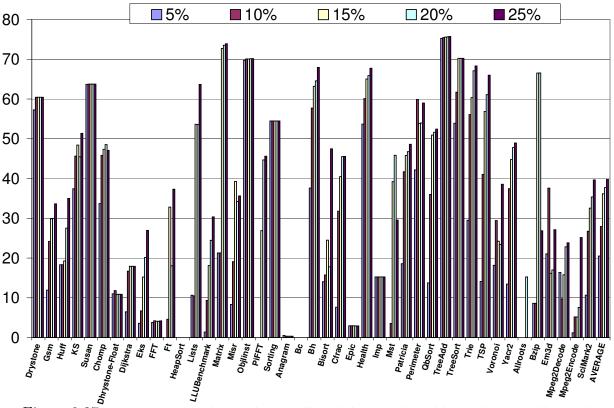

| 9.8  | Effect of varying SPM size on runtime gain using our approach 235            |

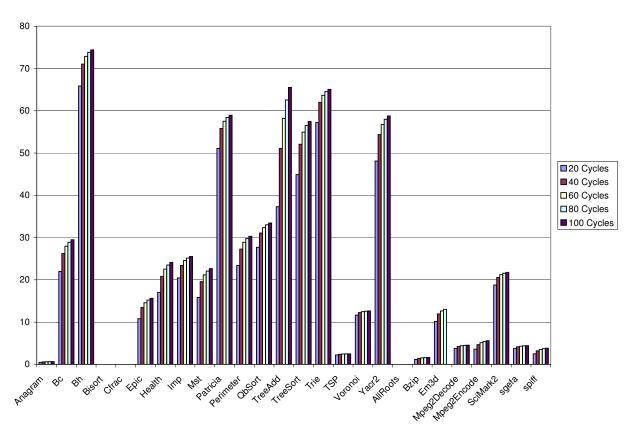

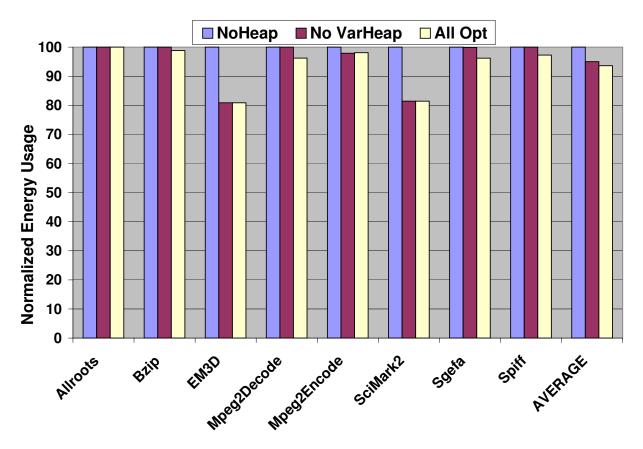

| 9.9  | Normalized runtime for unknown-size benchmark set                            |

| 9.10 | Normalized energy consumption for unknown-size benchmark set 237             |

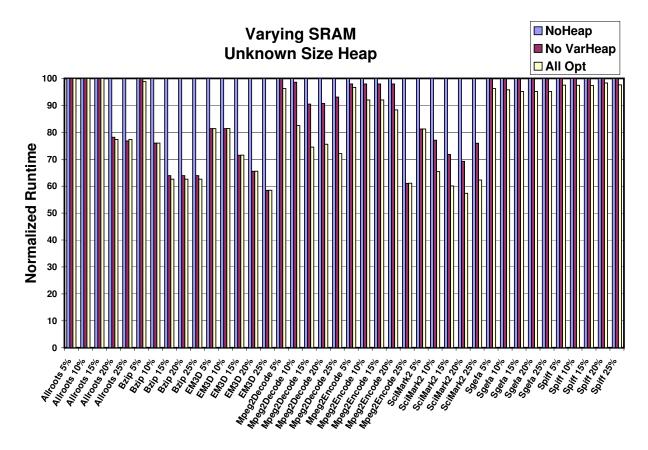

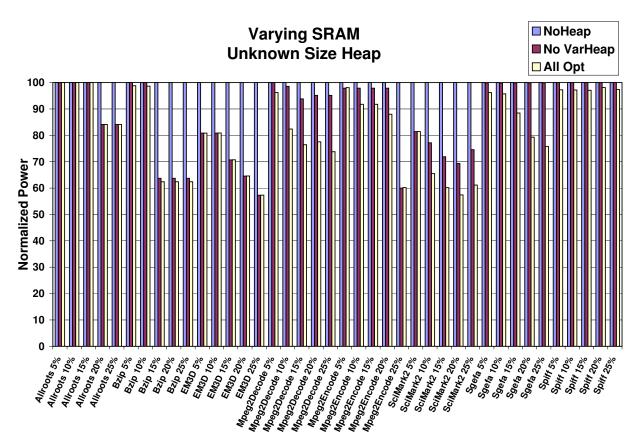

| 9.11 | Normalized runtime for unknown-size benchmark set when varying SPM size      |

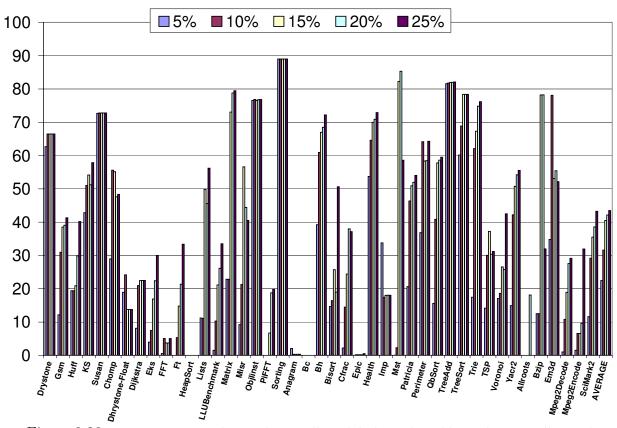

| 9.12 | Normalized energy usage for unknown-size benchmark set when varying SPM size |

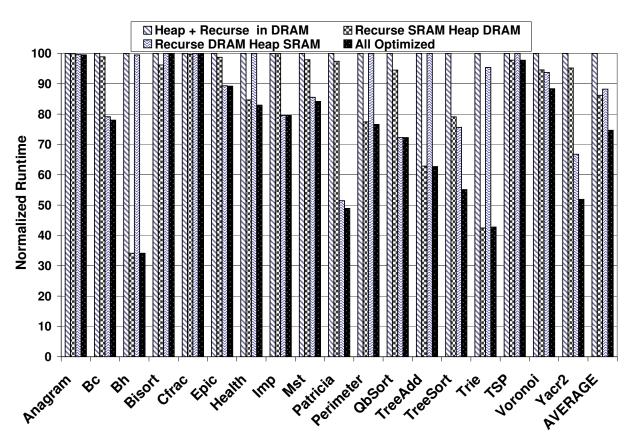

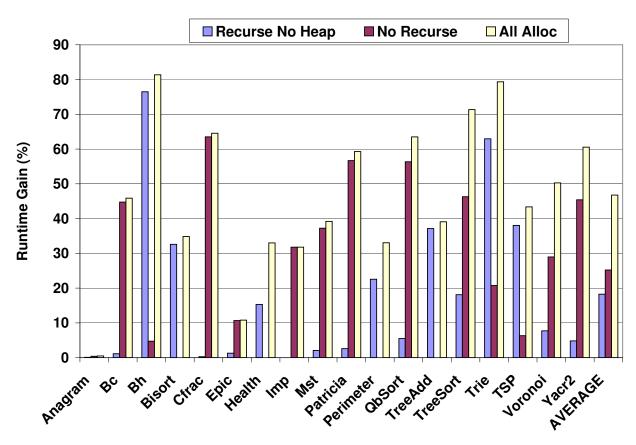

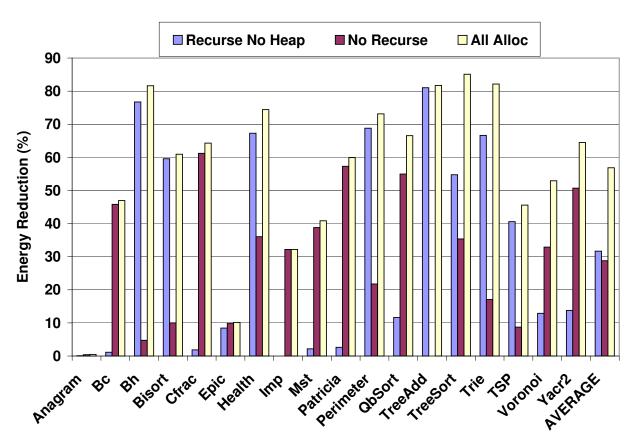

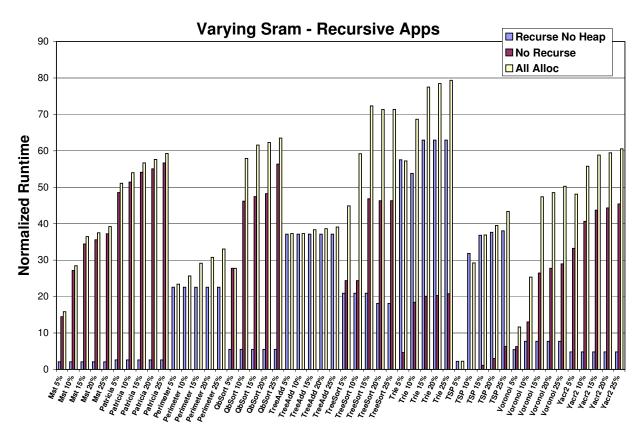

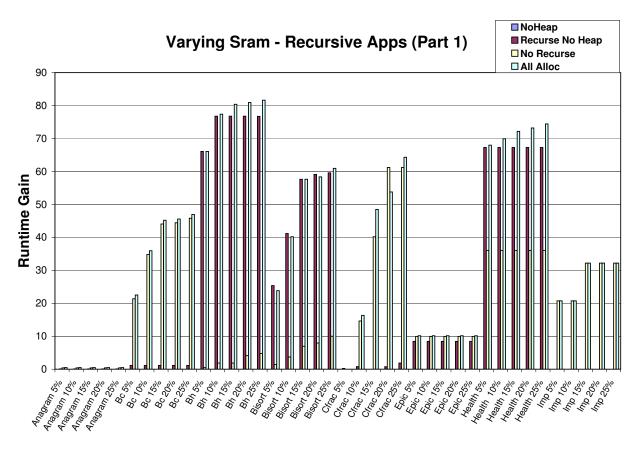

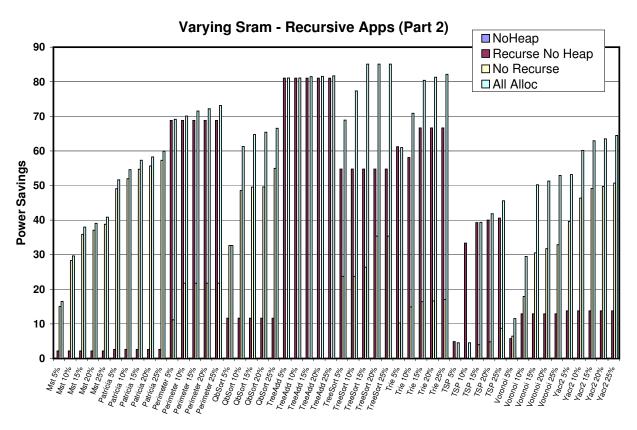

| 9.13 | Normalized runtime for recursive benchmark set                               |

| 9.14 | Reduction in energy consumption for recursive benchmark set 243              |

| 9.15 | Normalized runtime for recursive benchmark set at 25% SPM 245                       |

|------|-------------------------------------------------------------------------------------|

| 9.16 | Normalized energy usage for recursive benchmark set at 25% SPM. $$ . 246 $$         |

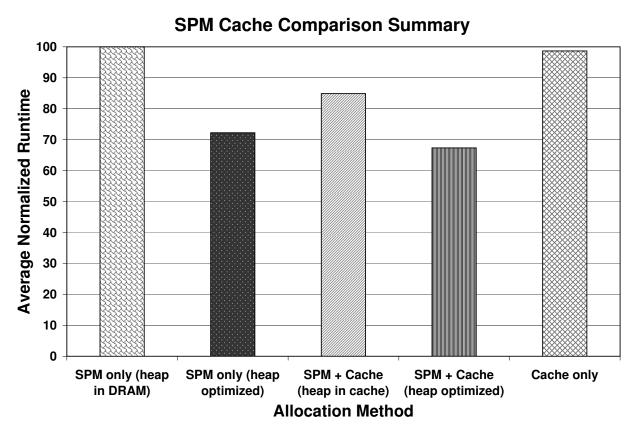

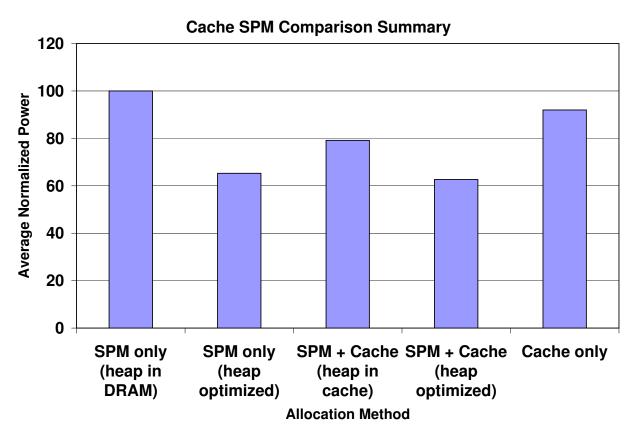

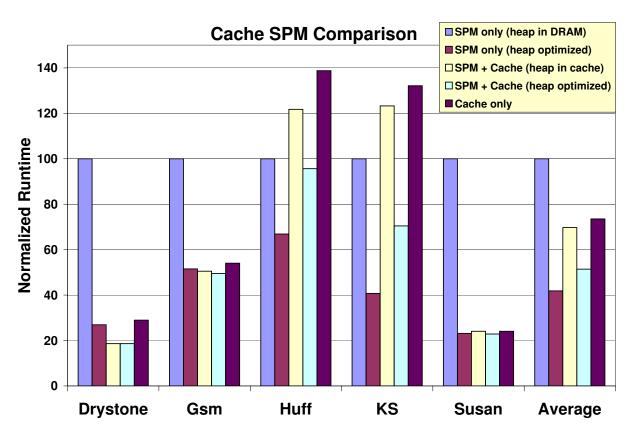

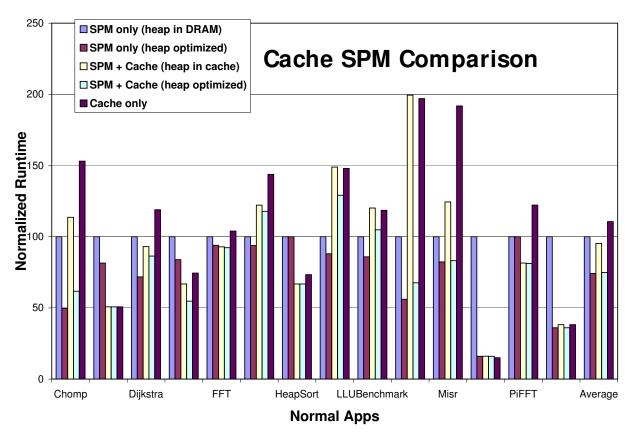

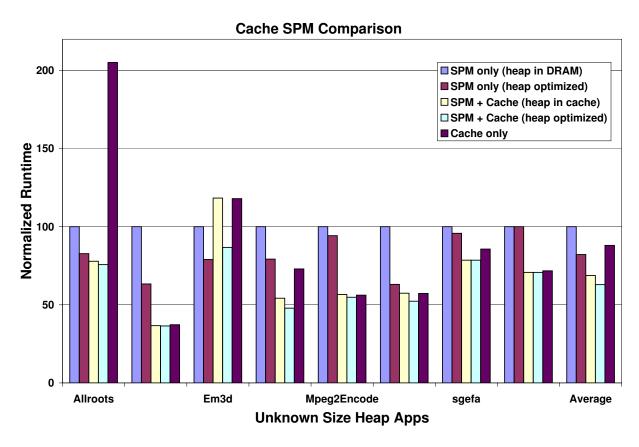

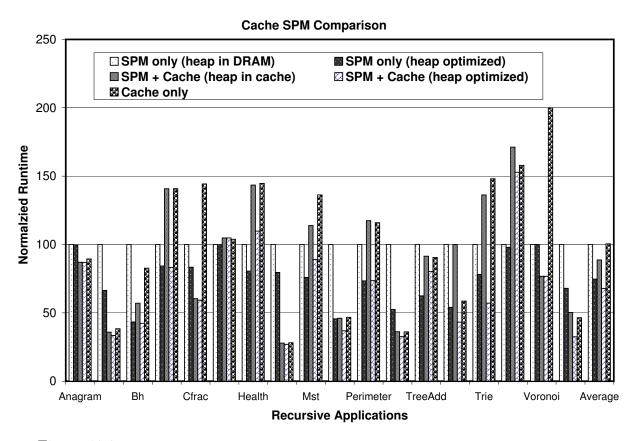

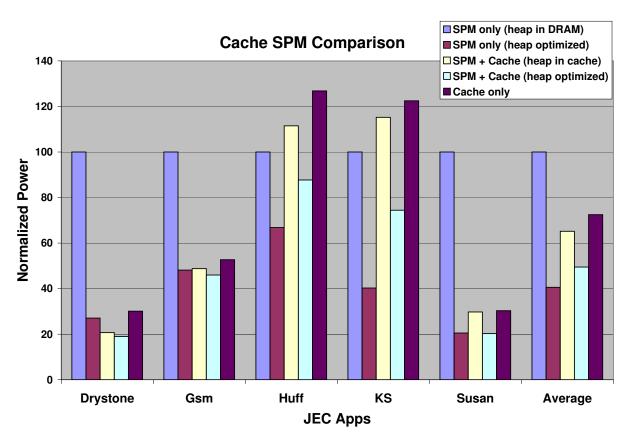

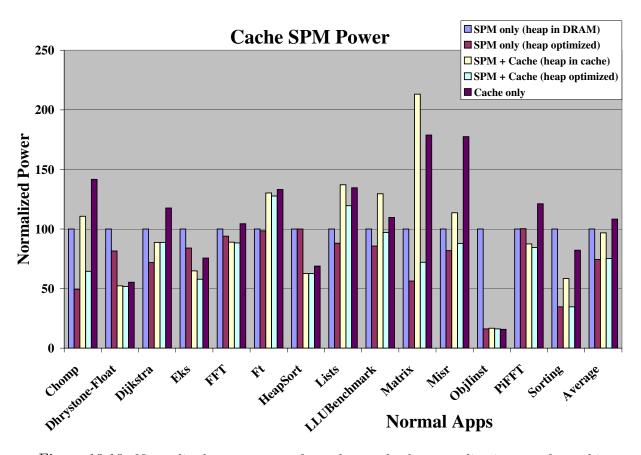

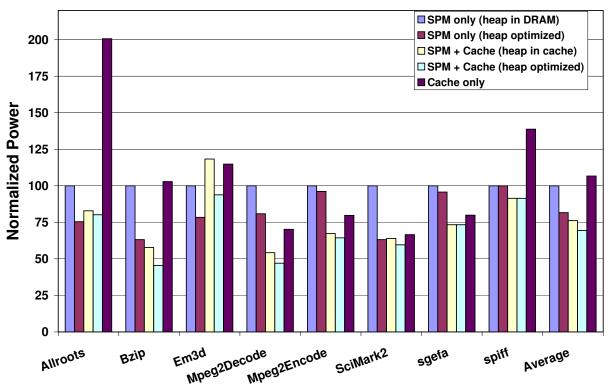

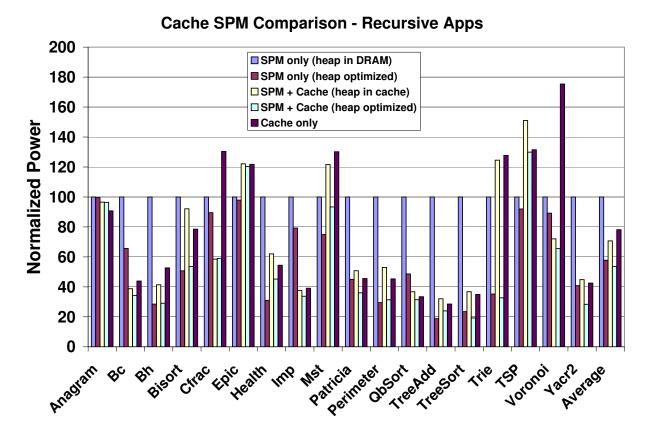

| 9.17 | Average normalized runtimes for benchmarks using combinations of SPM and cache      |

| 9.18 | Averaged normalized energy usage for benchmarks using combinations of SPM and cache |

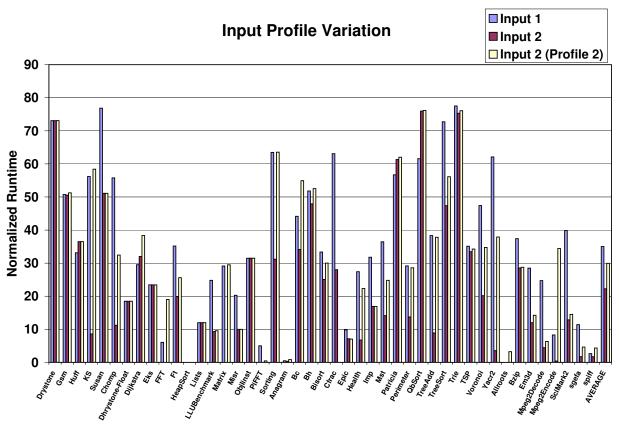

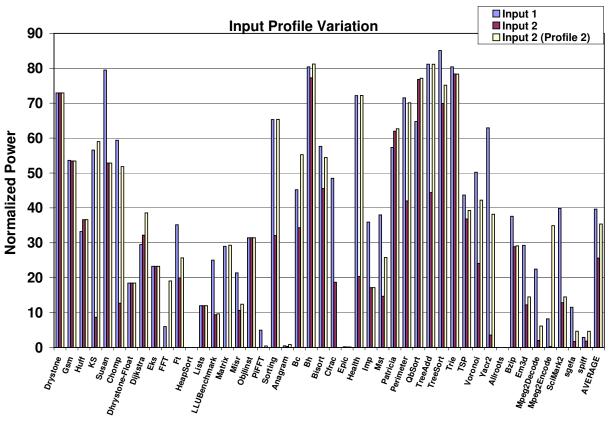

| 9.19 | Normalized runtimes for benchmarks using the second benchmark input set             |

| 9.20 | Normalized energy usage for benchmarks using the second benchmark input set         |

| 9.21 | Average runtime gain for benchmarks using both benchmark input sets                 |

| 9.22 | Average energy savings for benchmarks using both benchmark input sets               |

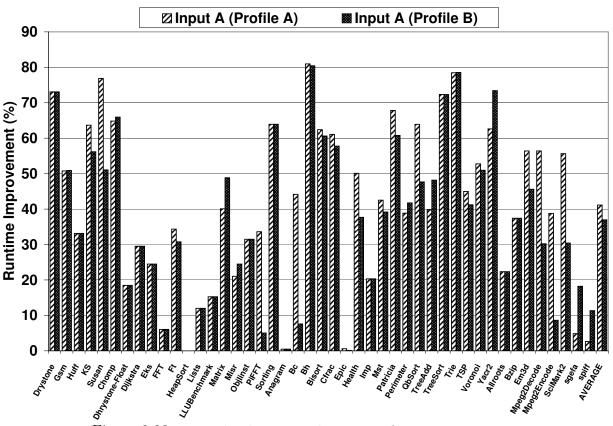

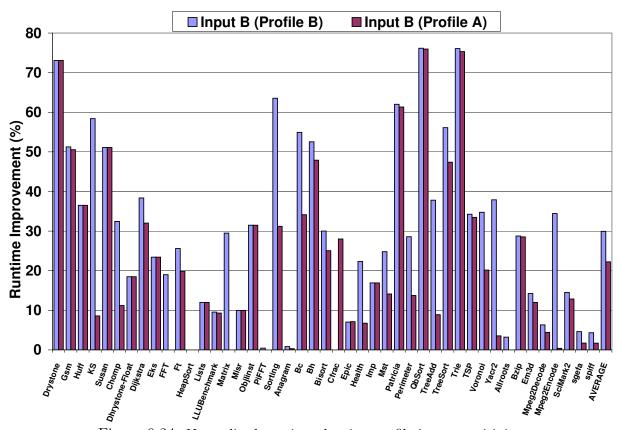

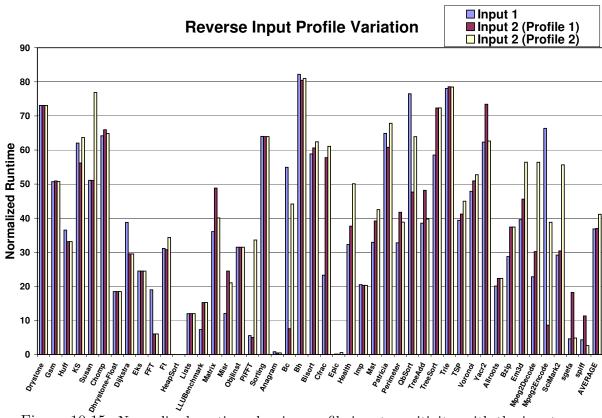

| 9.23 | Normalized runtime for benchmarks showing profile input sensitivity. 260            |

| 9.24 | Normalized energy usage for benchmarks showing profile input sensitivity            |

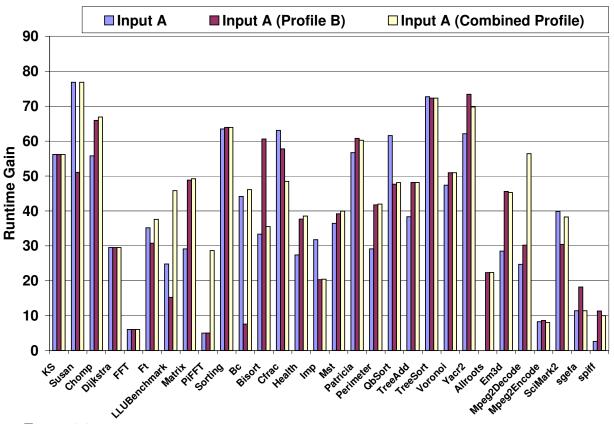

| 9.25 | Improvement in runtime from profile averaging passes                                |

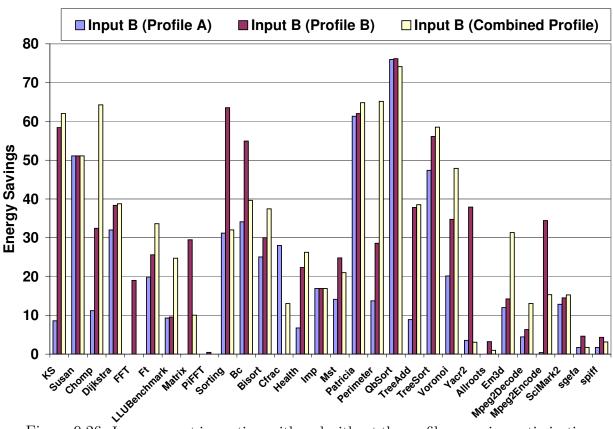

| 9.26 | Improvement in energy usage from profile averaging passes 263                       |

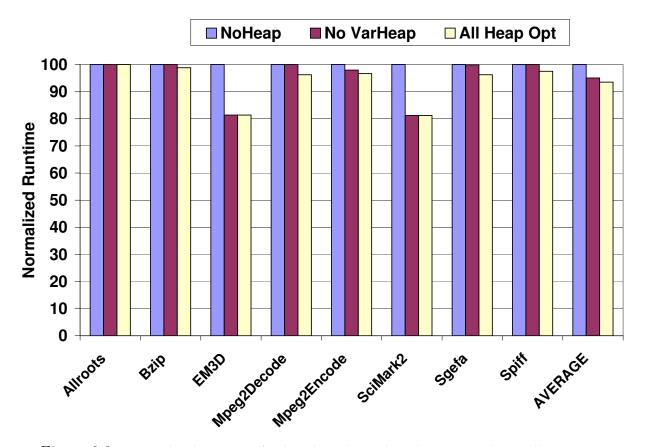

| 9.27 | Runtime gain when code as well as global, stack and heap data are allocated         |

| 9.28 | Energy savings when code as well as global, stack and heap data are allocated       |

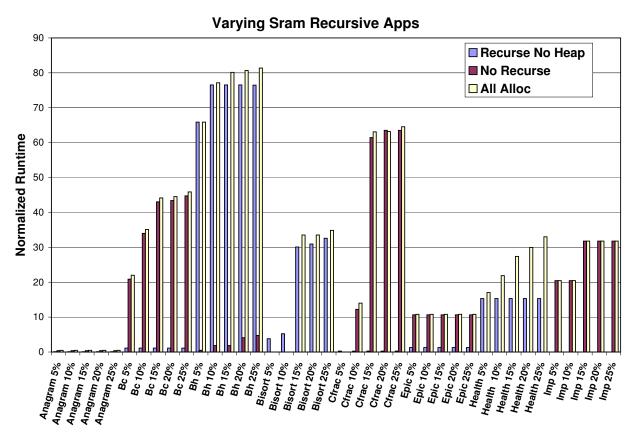

| 10.1 | Normalized runtime for recursive applications when SPM size varies(Part 1)          |

| 10.2 | Normalized runtime for recursive applications when SPM size varies<br>(Part 2)      |

| 10.3 | Normalized energy usage for recursive applications when SPM size varies(Part 1)     |

| 10.4 Normalized energy usage for recursive applications when SPM size varies(Part 2)                   | 273 |

|--------------------------------------------------------------------------------------------------------|-----|

| 10.5 Details on cache experiments with original JEC apps 2                                             | 274 |

| 10.6 Details on cache experiments with known-size heap benchmarks 2                                    | 275 |

| 10.7 Details on cache experiments with unknown-size heap benchmarks $2$                                | 276 |

| 10.8 Details on cache experiments with recursive benchmarks 2                                          | 277 |

| 10.9 Details on cache experiments with original JEC benchmarks 2                                       | 278 |

| 10.10Details on cache experiments with known-size heap benchmarks $2$                                  | 279 |

| 10.11Details on cache experiments with unknown-size heap benchmarks 2                                  | 280 |

| 10.12Details on cache experiments with recursive benchmarks 2                                          | 281 |

| 10.13Details on runtime gains from profile sensitivity experiments 2                                   | 282 |

| 10.14Details on energy savings from profile sensitivity experiments 2                                  | 283 |

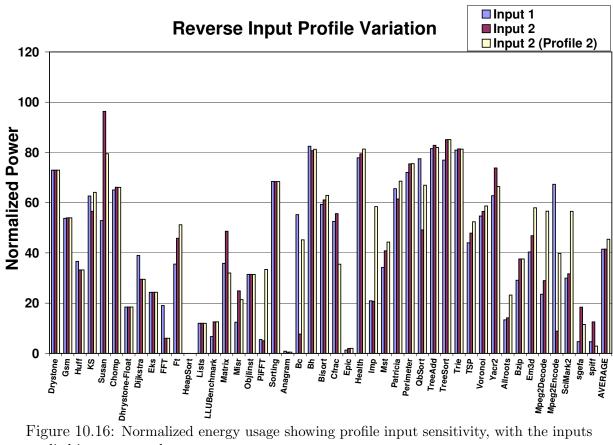

| 10.15 Details on runtime gains from profile sensitivity experiments when inputs are applied in reverse | 284 |

| 10.16Details on energy savings from profile sensitivity experiments when inputs are applied in reverse | 285 |

#### Chapter 1

#### Introduction

The proposed research presents an entirely new approach to dynamic memory allocation for embedded systems with scratch-pad memory. In embedded systems, program data is usually stored in one of two kinds of write-able memories – SRAM or DRAM (Static or Dynamic Random-Access Memories). SRAM is fast but expensive while DRAM is slower (by a factor of 10 to 100) but less expensive (by a factor of 20 or more). To combine their advantages, often a large DRAM is used to build low-cost capacity, and then a small SRAM is added to reduce runtime by storing frequently used data. The gain from adding SRAM is likely to increase in the future since the speed of SRAM is increasing by 60% a year versus only 7% a year for DRAM [64].

In desktops, the usual approach to adding SRAM is to configure it as a hard-ware cache. The cache dynamically stores a subset of the frequently used data. Caches have been a success for desktops – a trend that is likely to continue in the future. One reason for their success is that code compiled for caches is portable to different sizes of cache; on the other hand, code compiled for scratch-pad is usually customized for one size of scratch-pad. Binary portability is valuable for desktops, where independently distributed binaries must work on any cache size. In embedded systems, however, the software is usually considered part of the co-design of

the system: it resides in ROM or another permanent storage medium, and cannot be easily changed. Thus, there is really no harm to the binaries being customized to one memory size, as required by scratch pad. Source code is still portable, however: re-compilation with a different memory size is automatically possible in our framework. This is not a problem, as it is already standard practice to re-compile for better customization when a platform is changed or upgraded.

For embedded systems, the serious overheads of caches are less defensible. Caches incur a significant penalty in area cost, energy, hit latency and real-time guarantees. All of these other than hit latency are more important for embedded systems than desktops. A detailed recent study [17] compares caches with scratch pad. Their results are definitive: a scratch pad has 34% smaller area and 40% lower power consumption than a cache of the same capacity. These savings are significant since the on-chip cache typically consumes 25-50\% of the processor's area and energy consumption, a fraction that is increasing with time [17]. Even more surprising, the run-time cycle count they measured was 18% better with a scratch pad using a simple static knapsack-based [17] allocation algorithm, compared to a cache. Defying conventional wisdom, they found absolutely no advantage to using a cache, even in high-end embedded systems in which performance is important. With the superior dynamic allocation schemes proposed here, the run-time improvement will be larger. Given the power, cost, performance and real time advantages of scratch-pad, and no advantages of cache, it is not surprising that scratch-pads are the most common form of SRAM in embedded CPUs today (eg: [28, 4, 102, 135, 101]), ahead of caches. Trends in recent embedded designs indicate that the dominance of scratch-pad will likely consolidate further in the future [120, 17], for regular as well as network processors.

Although many embedded processors with scratch-pad exist, compiling program data to effectively use the scratch-pad has been a challenge. The challenge is different for static data like code, global and stack variables, on one hand, and dynamic data like heap and recursive stack variables, on the other. The basis of this difference lies in the fundamental nature of the two data types and how program behavior affects their utilization. This is explained below.

Recent advances have made much progress in compiling code, qlobal and stack variables into scratch-pad memory. Two classes of compiler methods for allocating these objects to scratch-pad exist. First, static allocation methods are those in which the allocation does not change at run-time; these include [16, 127, 66, 15, 126] and others not listed here. In such methods, the compiler places the most frequently used variables, as revealed by profiling, in scratch pad. Placing a portion of the stack variables in scratch-pad is not easy - [16] is the first method to solve this difficulty by partitioning the stack into two stacks, one for scratch-pad and one for DRAM. Second, recently proposed dynamic methods improve upon static methods by allowing variables to be moved at run-time [136, 132, 84, 140]. Being able to move variables enables tailoring the allocation to each region in the program rather than having a fixed allocation as in a static method. Dynamic methods aim to keep variables that are frequently accessed in a region in scratch-pad during the execution of that region. The methods in [136, 84] explicitly copy variables from DRAM into scratch-pad just before a region in which they are expected to the

frequently accessed. Other variables are evicted to DRAM by explicit copy out instructions to make space for incoming variables. Details concerning these and other existing methods relating to SPM allocation will be presented in Chapter 3.

Allocating dynamic data to scratch-pad has proven far more difficult. Indeed, as far as we know, no one has proposed a successful method to allocate a portion of a program's dynamic data to scratch-pad memory. To see why, it is useful to understand dynamic data and their available analysis techniques; an overview follows. We will focus on heap variables as the main focus of our methods although we have applied similar concepts for recursive stack objects (described later). Heap objects are allocated in programs by dynamic memory allocation routines, such as malloc in C and new in Java. They are often used to store dynamic data structures such as linked lists, trees and graphs in programs. Many compiler techniques for heap analysis group all heap objects allocated at a single site into a single heap "variable". Additional techniques such as shape analysis have aimed to identify logical heap structures, such as trees. Finally, in languages with pointers, pointer analysis [42, 129] is able to find all possible heap variables that a particular memory reference can access.

Having understood heap variables, let us consider why heap data is difficult to allocate to scratch-pad memory at compile-time. Two reasons for this difficulty are as follows. First, heap variables are usually of *unknown size* at compile-time. For example, linked lists, trees and graphs allocated on the heap typically have a data-dependent number of elements, and thus a compile-time-unknowable size. Thus it is difficult to guarantee at compile-time that the heap variable will fit in scratch-pad.

Such a guarantee is needed for a compiler to place that heap variable in scratch-pad. Second, moving data at run-time, as is required for any dynamic allocation method to scratch-pad, usually leads to the *invalid pointer problem* if the moved data is a heap object. To see why, consider that heap data often contains pointers to other heap data, such as the child pointers in a tree node. When a heap object is moved between scratch-pad and DRAM, all the pointers into it become invalid. Updating all these pointers at run-time is prohibitively expensive since it involves scanning through entire, possibly large, heap structures at each move. Static methods avoid this problem, but lack the better per-region customization of dynamic methods.

Lacking compile-time methods for heap allocation to scratch-pad, people have investigated run-time methods, *i.e.*, methods that decide what to place in scratch-pad only at run-time; however largely they have not been successful. Primary among run-time methods is software caching [100, 60]. This class of methods emulate the behavior of a hardware cache in software on the scratch-pad. Since caches decide their contents at run-time, software caching decides the subset of heap data to store in scratch-pad at run-time. Software caching is implemented as follows. A tag consisting of the high-order bits of the address is stored for each cache line in software. Before each load/store, additional instructions are compiler-inserted to mask out the high-order bits of the address, access the tag, compare the tag with the high-order bits and then branch conditionally to hit or miss code. Some methods are able to reduce the number of such inserted overhead instructions [100], but much of it remains, especially for non-scientific programs and for heap data. This implementation points to the primary drawbacks of software caching: the inserted

code before each load/store adds significant overhead, including (i) additional runtime; (ii) higher code size and dollar cost; (iii) higher data size and cost from tags; and (iv) higher power consumption. These overheads, especially for heap data, can easily exceed the gains from locality.

In conclusion, lacking compile-time methods and successful run-time methods for heap allocation to scratch-pad, heap data is usually not allocated to scratch-pad at all in modern embedded systems; instead it is placed entirely in DRAM.

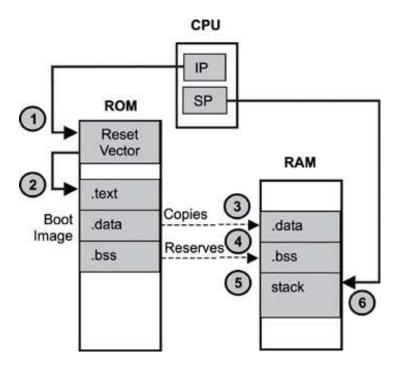

Heap allocation method This paper proposes a new dynamic method for allocating a portion of the heap to scratch-pad. The method is outlined in the following three steps. First, it partitions the program into regions such that the start and end of every procedure and every loop is the beginning of a new region, which continues until the next region begins. This is not the only possible choice of regions; the reasons for this choice are in section 5.3. Second, straightforward analysis is done to determine the time-order between the regions by finding the set of possible predecessors and successors of each region. Third, copying code is inserted by the compiler at the beginnings of regions to copy in portions of heap variables into the scratch-pad; these portions are called bins. A cost-model driven heuristic method is used to determine which variables to copy in and what size their bins should be.

At first glance, the above method is similar in flavor to our compile-time dynamic method for code, global and stack data [132] in that it copies in data when the compiler expects that it will be frequently used in the next region. However its real novelty is seen in how it solves the unknown size problem and the invalid data problem mentioned earlier. How these problems are solved result in virtually every

aspect of the algorithm being different from our earlier method. The solutions to the unknown size problem and the invalid data problem are described in the next two paragraphs.

First, our heap method solves the problem of unknown-size heap variables by **not** storing all the elements of a heap allocation site in its SRAM bin, but only a fixed-size subset. (From here on "site" is used to mean the objects allocated at a site). This fixed-size portion for each site in scratch-pad is called the bin for that site. Fixed-size bins make possible compile-time guarantees that they will fit in scratch-pad. For example consider a linked list having nodes of size 16 bytes and an unknown number of nodes. Here, the compiler may allocate a bin of size 192 bytes for the allocation site of the list – this will hold only 192/16 = 12 nodes from the list. The total number of nodes may be larger, but only twelve are allocated to the bin and the rest to DRAM. A bin is copied into SRAM just before every region where it is accessed (unless it is already in SRAM) and is subsequently evicted before a region where it is not <sup>1</sup>. When a bin is evicted it is maintained as a contiguous block in DRAM; it is copied back later to SPM contiguously if needed. This ensures that the offset of a particular data object inside its bin is not changed during its lifetime, regardless of whether the bin is in SRAM or DRAM.

It is important to understand that objects may be allocated or freed from either memory – separate free lists are maintained for each bin, and there is a unified free list for heap data that are not in bins. The bins are moved between

<sup>&</sup>lt;sup>1</sup>This is the default behavior but it is selectively changed for some regions by the optimizations in section 6.5.

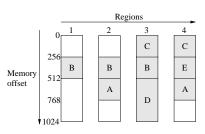

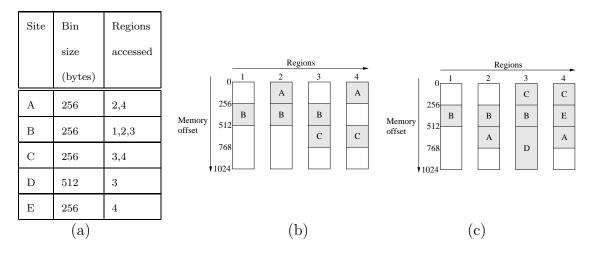

| Site  | Bin size | Regions  |  |

|-------|----------|----------|--|

|       | (bytes)  | accessed |  |

|       |          |          |  |

| A     | 256      | 2,4      |  |

| В     | 256      | 1,2,3    |  |

| С     | 256      | 3,4      |  |

| D     | 512      | 3        |  |

| E 256 |          | 4        |  |

| (a)   |          |          |  |

(b)

Figure 1.1: Example of heap allocation using our method showing (a) Heap Allocation sites for a program; (b) Memory layout of heap bins after allocation with our method.

SRAM and DRAM, but non-bin data is always in DRAM. New objects from a site are allocated to its bin if space is available, and to DRAM otherwise. Sites having a higher data re-use factor are assigned larger bins to increase the total run time gain from using bins. Figure 1.1(a) is an example showing the five allocation sites for a hypothetical program and bin size and regions-of-access for each site. Four regions 1-4 are assumed in the program, numbered in order of their timestamps (defined in section 5.3).

Second, our heap method solves the problem of invalid pointers by never changing the bin offset or size for any site in the regions it is accessed. For example, figure 1.1(b) shows the bin layout in scratch-pad for the sites in figure 1.1(a), for each of the four regions in the program. It shows that the offset of each bin is always the same when it is present. For example, site A is allocated at the same offset 512 in both regions 2 & 4 it is accessed. An entire bin may be evicted to DRAM in a region

it is not accessed (as revealed by pointer analysis). For example, site A is copied to DRAM in region 3. Moving a bin to DRAM temporarily results in invalid pointers that point to objects in the bin, but those invalid pointers are never dereferenced as they occur only during regions that pointer analysis has proven to not access the site.

Our heap method effectively improves run-time for three reasons. First, like a cache it allocates more frequently used data to SRAM. This is achieved by assigning larger bins to sites with high frequency-per-byte of access. Heap area is traded off with global and stack data as well – the frequency-per-byte of variables of all types (from profile data) are compared to determine which ones are actually copied to SRAM <sup>2</sup>. Any variable is placed in scratch-pad only if the cost model estimates that the benefits of locality exceed the cost of copying. Second, like caching our heap method is able to change the contents of the SRAM at runtime to match the requirements of different phases of the program. The allocation is dynamic, but is decided at compile-time. Third, unlike software caching, our method has no tags and no per-memory-access overhead.

Recursive Functions Recursion in computer programming defines a function in terms of itself. Recursion is deeply embedded in the theory of computation, with the theoretical equivalence of mu-recursive functions and Turing machines at the foundation of ideas about the universality of the modern computer. A good example application of recursion is in parsers for programming languages. The

<sup>&</sup>lt;sup>2</sup>The use of frequency-per-byte itself is not new. It has been used earlier for allocating global and stack variables to SPM [126, 111]. The novelty in this paper is in the solution to the unknown size and invalid pointer problems; this allows heap data to be placed in SPM.

great advantage of recursion is that an infinite set of possible sentences, designs or other data can be defined, parsed or produced by a finite computer program.

Unfortunately, even the best compiler analysis tools are unable to place a bound (except in trivial cases) on the total size of stack memory allocated by a recursive function at run-time, as it strictly depends on the inputs applied. This presents a serious problem for existing SPM allocation schemes which only handle static program data. Using concepts obtained from our methods for heap data allocation, we have developed the first methods able to allocate recursive stack functions to SPM at run-time. By treating individual function invocations like individual heap objects, we are able to make minor modifications to our framework to support recursive stack optimization. We will later present results showing significant improvements for applications making heavy use recursive functions.

Comparison with caches The primary measure of success of our heap method is **not** its performance vs. hardware caches, but vs. all-DRAM heap allocation, the only existing method for scratch-pad. (Software caching has not been a success). There are a great many chips that have scratch-pad memory (SPM) and DRAM but no data cache; examples include low-end CPUs [105, 6, 115], mid-grade CPUs [7, 14, 12, 67, 72] and high-end CPUs [8, 68, 104]. We found at least 80 such embedded processors with SPM and DRAM but no D-cache in our search but have listed only the above eleven for lack of space. Thus our method delivers its full promised benefits for a great variety of chips. It is nevertheless interesting to see a quantitative comparison of our method for SPM against a cache. Section 9.4 presents such a comparison. It shows that our compile-time method is comparable

to or out-performs a cache of the same area in both run-time and energy usage for our benchmark suite.

#### 1.1 Organization of Thesis

This thesis is organized in the following manner. The first four chapters constitute the background and related material for understanding the contributions of this thesis. Chapter 2 presents background material on embedded systems with a focus on typical hardware and software approaches for memory. The concept of static and dynamic data for compiler-based code optimization is also presented in this chapter. Chapter 3 presents a thorough review of recent research concerned with SPM allocation as well as related optimization concepts. Chapter 5 presents the best existing SPM allocation method for code, global and stack data, which is used in conjunction with our dynamic data method for a comprehensive program optimization approach. While the material in this chapter is not a new contribution from this thesis, it is presented as essential reading for a full understanding of our allocation methods.

The main contributions of this thesis are presented in Chapters 5–7. We have decided to first present our core method for optimizing typical heap data before expanding on this for our handling of other types of dynamic data. We present our core method for analyzing and understanding heap data in Chapter 5. Chapter 6 presents a step-by-step explanation of our algorithm for SPM allocation. Once the core method for heap data has been presented, Chapter 7 completes our presentation

with discussion of the extensions we have developed for all other program objects currently not handled by existing SPM allocation schemes.

The final four chapters of this thesis present our supporting material. Chapter 8 discusses the development and simulation methodology employed to properly host and evaluate our compiler methods. The results obtained from a wide range of experiments are presented in Chapter 9 with focus on interesting scenarios. Chapter 10 concludes the thesis by summarizing our findings. Finally, Chapter 10 is an appendix containing brief results of interest not explicitly discussed in Chapter 9.

#### Chapter 2

#### Embedded Systems and Software Development

This chapter will primarily present a brief review of those concepts on which we base our method for dynamic memory allocation of SPM for embedded systems. The chapter begins with a review of what exactly constitutes an embedded system, with emphasis placed on typical hardware configurations for these systems. This is followed by some background on the C programming language[43], which is by far the dominant language for embedded systems development. We will discuss both language and compiler specific material as they apply to optimizing memory allocation for compiled applications.

To perform optimal memory allocation for a program requires both knowledge of the program and information on the target machine that will execute the application. This in turn requires advanced compiler techniques involving many areas from both the hardware engineering and computer science disciplines. For example, in order for compilers to make the best decisions when creating intermediate implementations of high-level language programs, they require complete knowledge of the language being compiled and its associated memory and semantic details. Further, the final back-end requires lower-level information on the hardware and instructions available for a target platform in order to generate optimized assembly programs. This is a daunting task for modern compilers and developers to handle

in its entirety without some basic concepts in place. The following overview should help the reader understand the fundamentals behind our compiler directed memory allocation approach.

#### 2.1 Embedded Systems

At its simplest, an embedded system can be defined as any processing system that has been embedded inside of a larger product. For most engineers, embedded systems are more strictly defined as dependable, efficient, low-cost processing modules which are used as small components for a larger and more complicated technology. Regardless of the definition, embedded systems have become pervasive on modern society as advancements in technology have fostered an era of ubiquitous computing. Embedded devices have become a part of everyday life for most people and compose critical components in products such as automobiles, aircraft, mobile phones, media players and medical devices, among many more everyday objects. This proliferation in embedded systems has come about due to the advances in computer microprocessor technologies which have provided the boosts in size, complexity and efficiency needed.

As technology advanced, the exact definition of what constitutes an embedded system versus a traditional computer has become murky and difficult to pinpoint in some applications. General computing is generally divided among super-computers at its high-end and powerful servers and mainframes at its middle-level of performance. At the low-end of the traditional computer field lies the personal computer,

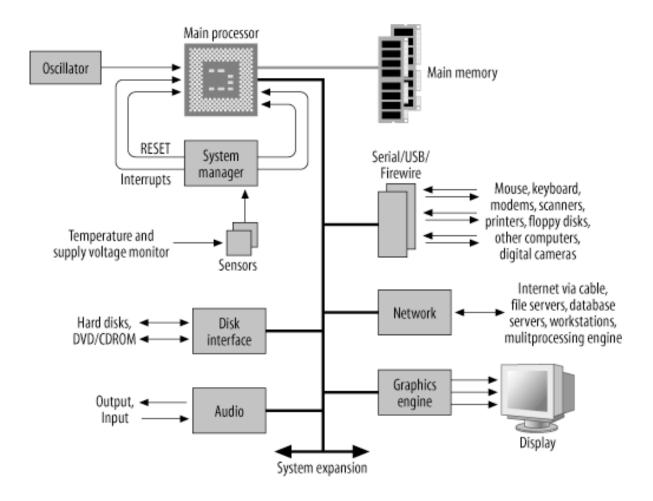

Figure 2.1: A block diagram view of a typical consumer computer.

most commonly found in the form of a desktop or laptop machine. A diagram of the components making up a typical consumer computer is shown in 2.1.

From this figure, a typical PC has a large main memory to hold the operating system, applications, and data, and an interface to mass storage devices (disks and DVD/CD-ROMs). It has a variety of I/O devices for user input (keyboard, mouse, and audio), user output (display interface and audio), and connectivity (networking and peripherals). The fast processor requires a system manager (BIOS) to monitor its core temperature and supply voltages, and to generate a system reset.

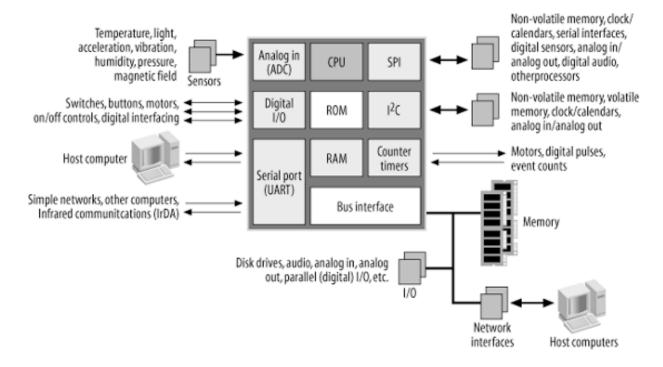

Figure 2.2: A block diagram view of a typical embedded computer.

Large-scale embedded computers may also take the same form. For example, they may act as a network router or gateway, and so will require one or more network interfaces, large memory, and fast operation. They may also require some form of user interface as part of their embedded application and, in many ways, may

simply be a conventional computer dedicated to a specific task. Thus, in terms of hardware, many high-performance embedded systems are not that much different from a conventional desktop machine.

Smaller embedded systems use microcontrollers as their processor, with the advantage that this processor will incorporate much of the computer's functionality on a single chip. An arbitrary embedded system, based on a generic microcontroller, is shown in Figure 2.2. The microcontroller has, at a minimum, a CPU, a small amount of internal memory (ROM and RAM), and some form of I/O, which is implemented within a microcontroller as subsystem blocks. These subsystems provide the additional functionality for the processor and are common across many processors.

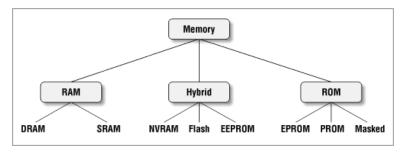

Many types of memory devices are available for use in modern computer systems. Most software developers think of memory as being either random-access (RAM) or read-only (ROM). Not only are there several distinct subtypes of each but the past decade has seen an upsurge of a third class of hybrid memories. In a RAM device, the data stored at each memory location can be read or written as desired. In a ROM device, the data stored at each memory location can be read at will, but never written. In some cases, it is possible to overwrite the data in a ROM-like device. Such devices are called hybrid memories because they exhibit some of the characteristics of both RAM and ROM. Figure 2.1 provides a classification system for the memory devices that are commonly found in embedded systems.

**Types of RAM** There are two important memory devices in the RAM family: SRAM and DRAM. The main difference between them is the lifetime of the data

Figure 2.3: Memory types commonly used in embedded systems.

stored. SRAM (static RAM) retains its contents as long as electrical power is applied to the chip. However, if the power is turned off or lost temporarily then its contents will be lost forever. DRAM (dynamic RAM), on the other hand, has an extremely short data lifetime-usually less than a quarter of a second. This is true even when power is applied constantly, which is typically the case for DRAM memory organizations. DRAM thus tends to incur a much higher power as well as access time due to its design.

When deciding which type of RAM to use, a system designer must also consider access time and cost. SRAM devices offer extremely fast access times (approximately four times faster than DRAM) but are much more expensive to produce. Generally, SRAM is used only where access speed is extremely important. A lower cost per byte makes DRAM attractive whenever large amounts of RAM are required. Many embedded systems include both types: a small block of SRAM (a few hundred kilobytes) along a critical data path and a much larger block of DRAM (in the megabytes) for everything else.

**Types of ROM** Memories in the ROM family are distinguished by the methods used to write new data to them (usually called programming) and the number

of times they can be rewritten. This classification reflects the evolution of ROM devices from hardwired to one-time programmable to erasable-and-programmable. A common feature across all these devices is their ability to retain data and programs physically and not electronically, saving information even when power is not applied.

The very first ROMs were hardwired devices that contained a preprogrammed set of data or instructions. The contents of the ROM had to be specified before chip production, so the actual data could be used to arrange the transistors inside the chip. Hardwired memories are still used, though they are now called "masked ROMs" to distinguish them from other types of ROM. The main advantage of a masked ROM is its low production cost. Unfortunately, the cost is low only when hundreds of thousands of copies of the same ROM are required and used to store data that will never be modifiable.

One step up from the masked ROM is the PROM (programmable ROM), which is purchased in an unprogrammed state. The process of writing data to a PROM involves the use of specialized device programming hardware. The programmer attaches to the PROM device and writes data to the device one word at a time by applying electrical charges to the input pins of the chip. Once a PROM has been programmed this way, its contents can never be changed as the electrical charges fuse the internal transistor logic gates open or closed. If the code or data stored in the PROM must be changed, the current module must be discarded and replaced with a new memory module. As a result PROMs are also known as One-Time Programmable (OTP) devices.

An EPROM (Erasable-and-Programmable ROM) is a memory type that is

programmed in the same manner as a PROM, but that can be erased and reprogrammed repeatedly. Depending on the silicon production process involved, these memory modules are created using different structures able to store data bits in the chip wafer that can also be reset using external stimuli in the form of radiation. Like PROMs, EPROMs must be erased completely and programming occurs on the entire contents of memory each time. Though more expensive than PROMs, their ability to be reprogrammed makes EPROMs an essential part of the software development and testing process as well as for firmware which will be upgraded occasionally.

Hybrid Types As memory technology has matured in recent years, the line between RAM and ROM devices has blurred. There are now several types of memory that combine the best features of both. These devices do not belong to either group and can be collectively referred to as hybrid memory devices. Hybrid memories can be read and written as desired, like RAM, but maintain their contents without

EEPROMs are electrically-erasable-and-programmable. Internally, they are similar to EPROMs, but the erase operation is accomplished electrically, rather than by exposure to more cumbersome methods like ultraviolet light. Any byte within an EEPROM can be erased and rewritten individually instead of requiring the entire module to be formatted. Once written, the new data will remain in the device forever-or at least until it is electrically erased. The trade-off for this improved functionality is mainly its higher cost. Write cycles are also significantly longer than writes to a RAM, rendering EEPROM a poor choice for main system

electrical power, just like ROM. Two of the hybrid devices, EEPROM and Flash, are

descendants of ROM devices; the third, NVRAM, is a modified version of SRAM.

memory.

Flash memory is the most recent advancement in memory technology. It combines all the best features of the memory devices described thus far. Flash memory devices are high density, low cost, nonvolatile, fast (to read, but not to write), and electrically reprogrammable. These advantages are overwhelming and the use of Flash memory has increased dramatically in embedded systems as a direct result. From a software viewpoint, Flash and EEPROM technologies are very similar. The major difference is that Flash devices can be erased only one sector at a time, not byte by byte. Typical sector sizes are in the range of 256 bytes to 16 kilobytes. Despite this disadvantage, Flash is much more popular than EEPROM and is rapidly displacing many of the ROM devices as well.

The third member of the hybrid memory class is NVRAM (nonvolatile RAM). Non-volatility is also a characteristic of the ROM and hybrid memories discussed earlier. However, an NVRAM is physically very different from those devices. An NVRAM is usually just an SRAM with a battery backup. When the power is turned on, the NVRAM operates just like any other SRAM. But when the power is turned off, the NVRAM draws just enough electrical power from the battery to retain its current contents. NVRAM is fairly common in embedded systems. However, it is very expensive-even more expensive than SRAM-so its applications are typically limited to the storage of only a few hundred bytes of system-critical information that cannot be stored in any better way.

We summarize our review of common embedded memory technologies with a table comparing their distinguishing features in Figure 2.1.

| Memory Type | Volatile? | Writeable?            | Erase Size  | Erase Cycles        | Relative Cost | Relative Speed              |

|-------------|-----------|-----------------------|-------------|---------------------|---------------|-----------------------------|

| SRAM        | yes       | yes                   | byte        | unlimited           | expensive     | fast                        |

| DRAM        | yes       | yes                   | byte        | unlimited           | moderate      | moderate                    |

| Masked ROM  | no        | no                    | n/a         | n/a                 | inexpensive   | fast                        |

| PROM        | no        | once, with programmer | n/a         | n/a                 | moderate      | fast                        |

| EPROM       | no        | yes, with programmer  | entire chip | limited (see specs) | moderate      | fast                        |

| EEPROM      | no        | yes                   | byte        | limited (see specs) | expensive     | fast to read, slow to write |

| Flash       | no        | yes                   | sector      | limited (see specs) | moderate      | fast to read, slow to write |

| NVRAM       | no        | yes                   | byte        | none                | expensive     | fast                        |

Figure 2.4: Comparison of the salient features for memory types common to embedded systems.

#### 2.2 Intel StrongARM Microprocessor

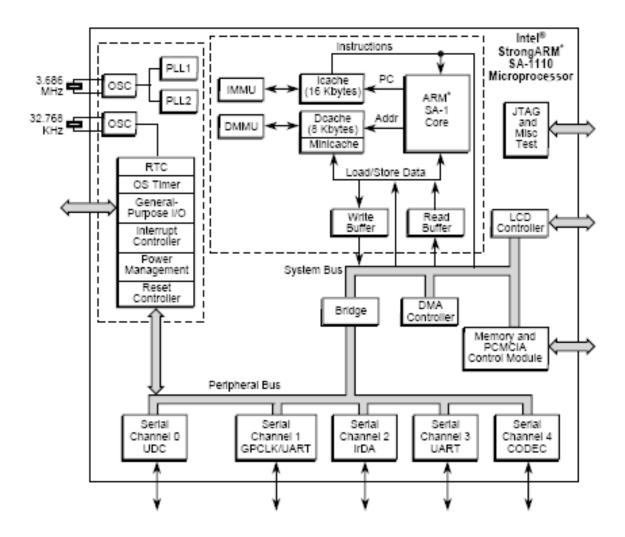

Having overviewed memory designs in the previous section, this section will now discuss the hardware organization of a typical embedded processor. As a case study, an example processor from the Intel StrongARM family will be highlighted in this section and used throughout the rest of the thesis as our reference platform. The Intel StrongARM Microprocessor (SA-1110) is a highly integrated communications microcontroller that incorporates a 32-bit StrongARM RISC processor core, system support logic, multiple communication channels, an LCD controller, a memory and PCMCIA controller, and general-purpose I/O ports. The SA-1110 provides power efficiency, low cost, and high performance in an embedded package with flexible memory options. Typical embedded deployments will contain a StrongARM cpu along with a variety of memory configurations, such as a cache(SRAM) with DRAM as main memory, or an SPM-only system with only an SPM(SRAM) module as main memory (cache modules disabled). Figure 2.5 shows a block diagram of the component modules for the SA-1110.

Figure 2.5: Block diagram for an Intel StrongARM within a complete embedded system.

The SA-1110 is a general-purpose, 32-bit RISC microprocessor with a clock speed adjustable up to 206 MHz. The embedded processor has a configurable instruction and data cache, memory-management unit (MMU), and read/write buffers for efficient data processing. The memory bus interfaces to many device types including SRAM(SPM), synchronous DRAM (SDRAM) and Flash(EEPROM). The StrongARM is software compatible back to the ARM V4 architecture processor family and can be used with ARM coprocessor chips such as I/O, memory, and video components. The ARM instruction set is a good target for compilers of many different high-level languages. Where required for critical code segments, assembly code programming is also straightforward, unlike some RISC processors that need sophisticated compiler technology to manage complicated instruction interdependencies. The SA-1110 has been designed to run at a reduced voltage to minimize its power requirements. This makes it a good choice for portable applications where both of these features are essential.

Deployments using the StrongARM processor can choose from memory modules such as DRAM or SRAM to use as main memory, as well as FLASH for code storage. All memory modules are cacheable in the StrongARM using its on-board cache hardware. The SA-1110 contains a 16 Kb instruction cache as well as an 8Kb data cache. Each module can be enabled or disabled via a control register, with fine-grain management available using the MMU to control which addresses are cacheable. Deployments concerned with power and realtime guarantees often choose to disable the cache modules and operate the device using only SRAM and ROM modules.

Embedded Design Trends The StrongARM was designed with the same goals as all other embedded processors, from low-end 8-bit and 16-bit processors that may cost less than a dollar, to high-end embedded processors (that can execute a billion instructions per second and cost hundreds of dollars) for the newest portable video game system. All embedded systems are ultimately designed to be cheap, fast and power-efficient. Although the range of computing power in the embedded computing market is very large, price is a key factor in the design of computers for this space. Performance requirements do exist, of course, but the primary goal is often meeting the performance need at a minimum price, rather than achieving higher performance at a higher price.

Two other key characteristics exist in many embedded applications: the need to minimize memory and the need to minimize power. In many embedded applications, the memory can be substantial portion of the system cost, and memory size is important to optimize in such cases. Sometimes the application is expected to fit totally in the memory on the processor chip; other times the applications needs to fit totally in a small off-chip memory. In any event, the importance of memory size translates to an emphasis on code size, since data size is dictated by the application. Larger memories also mean more power, and optimizing power is often critical in embedded applications. When hardware methods alone are insufficient, designers can still turn to software-only and hybrid methods to squeeze the most performance from embedded hardware to reduce cost and power while maximizing performance.

#### 2.3 Embedded Software Development

One of the few constants across almost all embedded systems is the use of the C programming language. More than any other, C has become the language of embedded programmers. This has not always been the case, and it will not continue to be so forever. However, at this time, C is the closest thing there is to a standard in the embedded world. Because successful software development is so frequently about selecting the best language for a given project, it is surprising to find that one language has proven itself appropriate for both 8-bit and 64-bit processors; in systems with bytes, kilobytes, and megabytes of memory; and for development teams that consist of from one to a dozen or more people. Yet this is precisely the range of projects in which C has thrived.

Of course, C is not without advantages. It is small and fairly simple to learn, compilers are available for almost every processor in use today, and there is a very large body of experienced C programmers. In addition, C has the benefit of processor-independence, which allows programmers to concentrate on algorithms and applications rather than on the details of a particular processor architecture. However, many of these advantages apply equally to other high-level languages, which has led many researchers in embedded systems to wonder why has C succeeded where so many other languages have mostly failed.

Perhaps the greatest strength of C, and what sets it apart from languages like Java, C++, Pascal and FORTRAN, is that C is a very "low-level" high-level language. As we shall see throughout the book, C gives embedded programmers

an extraordinary degree of direct hardware control without sacrificing the benefits of high-level languages. The "low-level" nature of C was a clear intention of the language's creators. In fact, Kernighan and Ritchie included the following comment in the opening pages of their book The C Programming Language:

C is a relatively "low level" language. This characterization is not pejorative; it simply means that C deals with the same sort of objects that most computers do. These may be combined and moved about with the arithmetic and logical operators implemented by real machines.

Few popular high-level languages can compete with C in the production of compact, efficient code for almost all processors. And, of these, only C allows programmers to interact with the underlying hardware so easily. The two other popular languages in use today for desktop and high-end embedded systems are C++ and Java. Both are object-oriented programming (OOP) languages which are more sophisticated than the C language in some ways, but that very complexity tends to be problematic for embedded systems development. Java and many other OOP languages enforce the use of garbage collectors to manage dynamically allocated memory. Garbage collectors greatly decrease the real-time guarantees for that system, an important consideration for many embedded designers. One of the other strengths of OOP languages lies in their abstraction of programs in terms of objects, which in turn requires more layers of translation during compilation to produce machine code. While allowing for more powerful and concise programming, these layers cause a disconnect when programming an embedded system that requires low-level

control over addressing to correctly use memory mapped devices, data allocation that is known and completely controllable by the programmer, as well as a myriad of low-level software interactions designers must employ when working with limited hardware platforms.

C-Language Allocation Basics Having understood some of the reasons for C's popularity in embedded development, a discussion of how C handles data allocation of program variables is also beneficial to understanding how compilers translate a C program into final machine code for a target processor. Traditional programming languages such as C and C++ maintain a list of attributes for each variable declared that minimally consists of its name, type, size, value, storage class, scope and linkage. Fundamental variable types and sizes are specified by that language's implementation, with names and values specified through user assigned identifiers in a valid program. Variable types in a language define its size, use and operator definitions for correct statement construction in a programming language. After a programmer declares a variable instance to possess a certain name and type, the instance declaration will also require a storage class specifier which dictates how its processed by the compiler for data allocation in the final machine code.

A variable's storage class specifier determines its storage class, scope and linkage in a compiler. The storage class also determines the lifetime of a variable during execution since variables can exist briefly, be repeatedly created and destroyed or exist and live throughout the entirety of program execution. The automatic storage class has automatic storage duration, and will create a declared variable when its declaration block is entered, exist while its active and destroy the variable once

the block has been exited. Local variables declared inside functions have automatic storage duration by default. The static storage class includes those variables and functions which exist from the point at which the program begins execution. For variables, storage is allocated and initialized upon beginning program execution and for functions the name of the function exists from program inception in a global symbol table. Although static duration variables and functions are created and exist throughout the entire program, their particular scope in the C-language will determine whether they may actually be referenced at any given point during program execution and the machine code generated will also reflect this.

Having looked at how the C-language dictates requirements for the compiler generation of program memory objects, we can now give a higher-level programmer view of C language memory objects which most people will be familiar with. Global variables are created by placing variable declarations outside any function definition by the compiler, and they retain their values throughout execution of the program. Global variables and functions can be referenced by any function that follows their declarations or definitions in the file. This is one of the main reasons for specifying function prototypes in included definition files such as 'stdlib.h', which allows the programmer to use a function interface properly even if that function body is present in another source file. This becomes of extreme importance when multiple source files are to be compiled together to produce an executable, as even a single source file program will likely use functions implemented in a system library file provided for low-level I/O support. A compiler must be able to differentiate between local and included source instance identifiers for program elements, and know how to

link separately compiled bundles of code together properly to produce a working executable. For any serious high-level implementation, this becomes of paramount importance and proper use of 'extern' and 'static' identifiers allow programmer's control over individual components as they relate to each other across multiple source files. By declaring a variable instance as 'extern', this tells the compiler that the variable exists in another file that will be included in the final program by the linker. Similarly, external function prototypes allow the linker to find the proper function implementation in another compiled object file.

The other static duration identifier is appropriately named 'static', and is most commonly used for local variable declarations which need to retain their values and storage throughout program execution. Local variables declared static are still bound to their local function scope, but retain their value when the function is exited and still available the next time it is entered. Local variables that are not declared static will be created upon entering a block with an initial value if specified and destroyed upon leaving that block. Static takes on further meaning when applied in a multi-file program being compiled. Normally global variables and functions have external linkage and can be accesses from other files if those files contain proper declarations and function prototypes. By adding the 'static' keyword to such declarations, this restricts the scope of such instances to the file in which if is defined, preventing its use by any function that is not defined in the same file. This allows a programmer to enforce the principle of least privilege in a C program, which consequently helps restrict compiler analysis to proper scopes and lifetimes as specified.

An important component of a declared data type concerns variable scope, which determines from where in the program that variable's identifier can be referenced correctly. For example, when a local variables is declared in a block, it can be referenced only in that block or in blocked nested within that program block. C provides function, file, block and function-prototype scope identifiers for a programmer to make use of. Only code labels have function scope and can be referenced anywhere inside the function they appear, but not outside of it. These generally appear in the form of case switches and 'goto' statements. Any variables declared outside a function have file scope, and their instances can be referenced from the point at which they are declared until the end of the file. Global variables, function declarations and function prototypes placed outside functions, such as include files, have file scope. Any variables declared inside a code block have block scope, denoted in C by enclosing the block inside of braces, eg: "{ int a; }". Local variables declared at the beginning of a function have block scope including the parameters passed to the function and any block can contain variable declarations. Any nested blocks that contain variables with the same instance names as those present in outer blocks will only reference the instances in the local block of scope. Even local variables that are declared static will only have block scope even though they exist from the time the program begins execution, illustrating that storage duration does not necessarily determine the scope of a variable. Finally, function-prototype scope only applies to the declarations inside the parameter list of a function prototype, for which the names are ignored but the types must match and function implementations in the file being compiled.

The largest and longest lived scope is that of global variables. Truly globally defined variables in C will have their label and associated memory requirement present in all files for a program being compiled, while those with only file-level scope will only be considered in scope for that file containing its declaration. The presence of procedures in the form of function blocks requires a more limited scope to be declared for stack variables while they are live. Locally scoped variables are those variables created for use by a function by occupying memory on the system's stack space. Creation of local stack variables occurs upon entering a procedure and are removed from the stack once it has been returned from or exited.

The nature of imperative languages such as C allow functions to call other functions, including themselves, and as execution progresses, a varying amount and number of locally scoped variables may live on the stack at any given time. These are not nearly as easy to predict and analyze for compiler optimization purposes as compared to global variables, since they may depend heavily on the control flow execution path dynamically taken through a program at run-time. Furthermore, compiler translation and optimization passes will affect how local variables are automatically created upon reaching their declaration block, and passes such as register allocation will decide final memory storage among registers and stack memory. On the other hand, global variables may be considered static in size and allocation terms, just as stack variables can be considered to be static in size and dynamic in allocation terms depending on the program path visited during execution.

The third and final type of variables in C are heap variables. When program's require a dynamic size and allocation method to efficiently handle inputs,

most platforms provide access to dynamic memory management systems through OS-level application calls. Dynamic memory managers maintain information on available free and used memory dedicated to heap memory. Indeed, the flexibility this buys programmers is in allowing size-efficient data structure creation as well as complete control over lifetimes of such structures that does not have to correlate with particular whole function lifetimes. This flexibility comes with a cost, and memory pointers must be used to access heap variables in addition to the memory management that must be performed explicitly by an operating system or another user program. Embedded systems usually require very fine-grain control over machine code running on limited hardware, so the loss of flexibility has minimal impact for most developers.

## 2.4 C Language Compilers

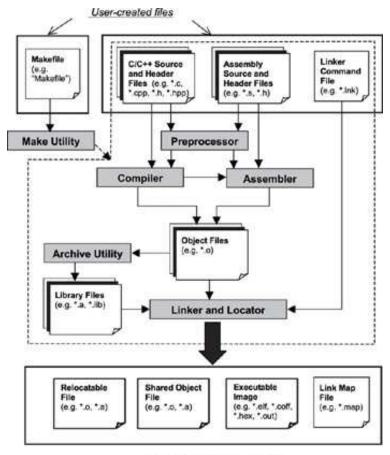

Figure 2.4 illustrates how a typical compiler platform can take various input files and generate appropriate output files to ultimately be used in building an executable image for a target processor. The developer writes the program in the C/C++ source files and header files. Some parts of the program can be written directly in assembly language when fine-grain control is needed, and are produced in the corresponding assembly source files. The developer creates a "Makefile" for use with the "make" utility to facilitate an environment that can easily track the file modifications and invoke the compiler and the assembler to rebuild the source files when necessary. From these source files, the compiler and the assembler produce

Linker generated output files

Figure 2.6: The typical compilation process for building an embedded executable from source files.

object files that contain both machine binary code and program data. The archive utility concatenates a collection of object files to form a library. The linker takes these object files as input and produces either an executable image or an object file that can be used for additional linking with other object files. The linker command file instructs the linker on how to combine the object files and where to place the binary code and data in the target embedded system.

The main function of the linker is to combine multiple object files into a larger relocatable object file, a shared object file, or a final executable image. In a typical program, a section of code in one source file can reference variables defined in another source file. A function in one source file can call a function in another source file. The global variables and non-static functions are commonly referred to as global symbols. In source files, these symbols have various names, for example, a global variable called "foobar" or a global function called "functionA". In the final executable binary image, a symbol refers to an address location in memory. The content of this memory location is either data for variables or executable code for functions.

Of course, each processor has its own unique ISA, so it is important to choose a compiler that is capable of producing programs for that specific processor. In the embedded systems case, this compiler almost always runs on a host computer. It simply does not make sense to execute the compiler on the embedded system itself. A compiler such as this-that runs on one computer platform and produces code for another-is called a cross-compiler. The use of a cross-compiler is one of the defining features of embedded software development. The GCC compiler and assembler can

be configured as either native compilers or cross-compilers. As cross-compilers these tools support an impressive set of host-target combinations including state of the art support for the ARM architecture.

The job of a compiler is mainly to translate programs written in some humanreadable language into an equivalent set of binary code for a particular processor. In that sense, an assembler is also a compiler but one that performs a much simpler one-to-one translation from one line of human-readable mnemonics to the equivalent binary opcode. There are good reasons for using a high-level language, yet programmers often write directly in assembly language. Assembly and machine code, because they are "hand-written," can be finely tuned to get optimum performance out of the processor and computer hardware. This can be particularly important when dealing with time-critical operations with I/O devices. Furthermore, coding directly in assembly can sometimes (but not always) result in a smaller code space. If a programmer is trying to cram complex software into a small amount of memory and needs that software to execute quickly and efficiently, assembly language may be their best (and only) choice. The drawback, of course, is that the software is harder to maintain and has zero portability to other processors. A good software engineer can create more efficient code than the average optimizing C compiler; however, a good optimizing compiler will probably produce tighter code than a mediocre assembly-language software engineer.

#### Compiler Optimization

Code optimization refers to the techniques used by a compiler to improve the execution efficiency of the generated object code. It involves a complex analysis of

the intermediate code and the performance of various transformations; but every optimizing transformation must also preserve the semantics of the program. A compiler should not attempt any optimization that would lead to a change in the program's semantics.

Optimization can be machine-independent or machine-dependent. Machineindependent optimizations can be performed independently of the target machine for which the compiler is generating code; the optimizations are not tied to the target machine's specific platform or language. Examples of machine-independent optimizations are elimination of loop invariant computation, induction variable elimination, and elimination of common subexpressions. Machine-dependent optimization requires knowledge of the target machine. An attempt to generate object code that will utilize the target machine's registers more efficiently is an example of machinedependent code optimization. The process of code optimization is somewhat of a misnomer; even after performing various optimizing transformations, there is no guarantee that the generated object code will be optimal. Hence, a compiler actually performs code improvement. When attempting any optimizing transformation, the following criteria should be applied. First, the optimization should capture most of the potential improvements without an unreasonable amount of effort. Second, the optimization should be such that the meaning of the source program is preserved. Finally, the optimization should, on average, reduce the time and space expended by the object code.

Code generation is the last phase in the compilation process. Being a machinedependent phase, it is not possible to generate good code without considering the details of the particular machine for which the compiler is expected to generate code. Even so, a carefully selected code-generation algorithm can produce code that is twice as fast as code generated by an ill-considered code-generation algorithm. Code generated by using simple statement-by-statement conversion strategies contain redundant instructions and suboptimal constructs. Therefore, to improve the quality of the target code, optimization is required. Peephole optimization is an effective technique for locally improving the target code. Short sequences of target code instructions are examined and replaced by faster sequences wherever possible. Other optimizations can account for larger regions of program code to perform transformations affecting different program areas, such as function inlining and outlining.

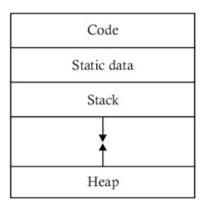

One of the important tasks that a compiler must perform is to allocate the resources of the target machine to represent the data objects that are being manipulated by the source program. That is, a compiler must decide the run-time representation of the data objects in the source program. Source program run-time representations of the data objects, such as integers and real variables, usually take the form of equivalent data objects at the machine level; whereas data structures, such as arrays and strings, are represented by several words of machine memory.

The strategies that can be used to allocate storage to the data objects are determined by the rules defining the scope and duration of the names in the programming language. The simplest strategy is static allocation, which is used in languages like FORTRAN. With static allocation, it is possible to determine the run-time size and relative position of each data object during compilation. A more-